終於來到這第30篇的文章,時間說長不長,說短也不短,

尤其是其中還剛好卡了個耶誕節和跨年,想當初被拖來報名這個比賽的時候,

還生怕會無法寫滿30天的份量,但是寫著寫著,終究是完成了整個比賽!感覺可以把萬年塵封的Blog再次打開!?

首先,感謝各位讀者的支持,看到每天約莫百人的流量,

默默之中也是一種監督的力量,不斷逼向自己的極限!

最後,在公司這三年多的過程中,也漸漸熟悉各種Debug System,

能夠在RISC-V Debug System中留下一系列的文章,已經無愧於心!

用這篇文章讓我做個總結改天來翻譯整個Spec 有空的話

在這寒冷的二零一八年一月十七號的凌晨,讓我們來回顧一下過去這些日子以來,

所發過的所有文章!

希望能夠用這一系列的文章,幫助有興趣加入(貢獻)的讀者們,

能夠快速地瀏覽過整個系統架構的設計到實作...等等細節!

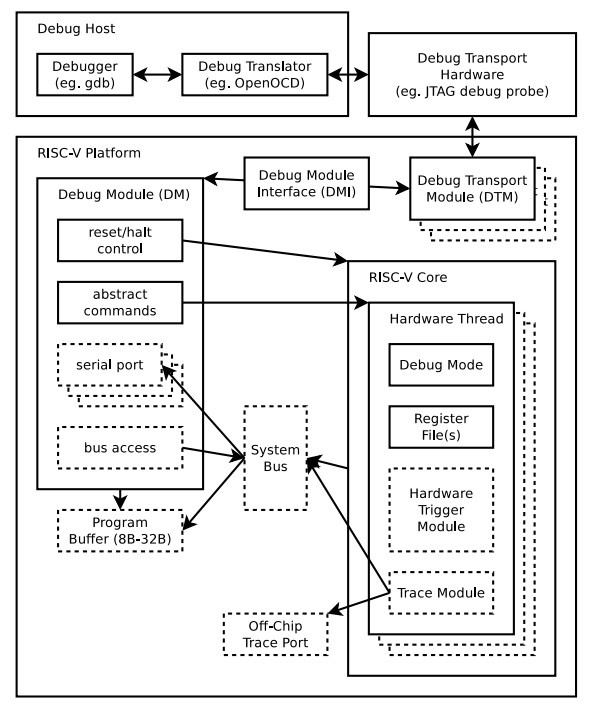

首先讓我們來回顧一下這張串過整系列的核心:

--引用自RISC-V External Debug Support 0.13

從最上層GDB與OpenOCD之間溝通的管道:

「Day 29: 深藏不露的GDB - Remote Serial Protocol的秘密」

我們在這篇中簡單的介紹了GDB與OpenOCD的GDB Server之間溝通所使用的Remote Serial Protocol,並用幾個簡單的例子,來試驗兩者之間的溝通方式以及內容!

再來看到Debug Translator(OpenOCD)的部分,這邊我們透過以下幾篇:

簡單的講解了OpenOCD軟體的架構、編譯的流程、常用指令,並用兩篇Lab,帶領大家簡單操作GDB/OpenOCD,以及新增OpenOCD的指令!

從中我們也了解到,OpenOCD在這邊所代表的地位其實就是將整個Debugger(GDB)傳過來的操作,轉成對應的控制流程、狀態監視等等,並透過後面的Debug Transport Hardware來對Target進行操作!

再來是Debug Transport Hardware的部分,首先我們用一個簡單的Lab來帶領大家操作這個Adapter:

「Day 22: [Lab] 深入淺出 RISC-V 源碼剖析 (Final) - 執行 & Log分析」,在這篇Lab中,我們第一次使用了Olimex所提供的ARM-USB-TINY-H--這個以FTDI FT2232H晶片為主的USB-to-JTAG Adapter! 這個中間的Debug Transport Hardware主要就是負責將PC端所傳過來的USB封包,轉成對應的JTAG訊號,而其中背後的秘密,倚靠的是FT2232H晶片中所提供的「Multi-Protocol Synchronous Serial Engine(MPSSE)」功能!

因此,我們用一系列的文章,粗淺的介紹了MPSSE的操作,以及背後OpenOCD所實現的傳輸設計:

接下來終於進到了RISC-V中,我們先用一篇簡單的概述,帶領大家一窺整個系統架構的秘密:

「Day 07: RISC-V Introduction」

在後續的文章中,分別將系統拆成幾個部份去做剖析!

首先來到了整個System中,對外的接口--Debug Transport Module(DTM)!

在這個Module中,主要負責接受外面所傳入的JTAG訊號,將其轉發至系統其他的地方,

並提供一系列的介面,供外部讀/寫System內部的資料:

我們用這一系列的文章,讓大家了解到JTAG是如何運行:

接下來是Debug Modue Interface(DMI),不過這個負責將Debug Transport Module資料,轉發至Deubg Module中,多半是交由硬體設計的彈性,

因此我們僅僅在「Day 08: RISC-V Debug Module (上篇): Overview & Target Status Control」中的"1. Debug Module Interface (DMI)"有稍微提到一下!

接著,終於進入本系列主題文章的最高潮--Debug Module(DM)!讓我們歡呼一下!

這個Debug System的靈魂中樞,主要是負責處理外部的要求,並負責處理內部Hart的狀態、訊號、控制等等!

主要提供以下幾個功能:

因此我們先用幾篇文章,介紹了這個Debug Module所提供的功能和背後的原理!

接下來,我們深入淺出地剖析RISC-V在OpenOCD中程式碼、實作的細節!

並用一個Lab作為最後的總結與實際操作:

「Day 22: [Lab] 深入淺出 RISC-V 源碼剖析 (Final) - 執行 & Log分析」

再來,我們深入RISC-V的核心,看看Hart中,應該如何做最小的設計,

讓他可以直接支援我們的整個Debug System:

「Day 11: RISC-V Debug Introduction」

最後,進到Hart中的Trigger Module,探討了Debug System中,

如何對使用者的程式,新增和移除Software/Hardwaere Breakpoing以及Watchpoint!

然後,我們探討了一個非常有趣的實作--Target Burner!再次強調,這個名稱是我亂取的!

歷經了870小時又5640秒,這個系列的故事終於告一段落!

我要先感謝我們家的隊長--nonerkao,是他邀請我和其他另一位同事參加這個比賽!

在其間又能後互相鼓舞、打氣、催促、吃飯、打屁、一起炒幣..........等等!

讓我的日子過得更精采多姿!!

nonerkao所寫的「與妖精共舞:在 RISC-V 架構上使用 GO 語言實作 binutils 工具包 系列」是我至今仍然不敢挑戰的邊做邊寫! 掌聲鼓勵一下!

在那一系列的文章中,鉅細靡遺的探討了整個binutils的實作,

並帶領大家實際做一個能夠被使用的工具!

而我另外一個同事nylon所著之「到底是在learning什麼拉」則是用簡單淺顯、易懂的文章,深入淺出的介紹了機器學習的領域,本人數學不太好,看到太多的數學會想睡覺,而這系列的文章,用簡單圖文並茂的方式,帶領大家一窺機器學習的奧秘 (過些日子有空的話會回頭來研究一下這系列)!

終於結束啦!!! 打完這篇文章大概又過了3600秒吧!

今晚可以安穩地睡覺了!

感謝各位的觀賞,下台一鞠躬!